Chap 6: Appendix: Storage, Networks and Other Peripherals⚓︎

约 1716 个字 预计阅读时间 9 分钟

核心知识

- I/O 设备

- 特点

- 与处理器和存储器的通信:轮询、中断、DMA

- 总线

- 各种类型

- 总线事务:输入、输出

- 同步 / 异步(握手协议)

- 总线仲裁

- 带宽

Introduction to I/O Devices⚓︎

设计输入 / 输出设备(I/O devices) 需要考虑以下因素:

- 可扩展性(expandability)

- 恢复力(resilience)

- 性能(performance)

- I/O 设备的性能难以评估,在不同情况下需要用不同的方法测量

- 决定因素:设备与系统之间的连接、内存层级、操作系统等

- 衡量指标:

- 吞吐量 (throughput)(即 I/O 的带宽 (bandwidth)

) :两种衡量方式:- 特定时间内在系统内传输的数据

- 单位时间内的 I/O 操作数

- 响应时间

- 吞吐量 (throughput)(即 I/O 的带宽 (bandwidth)

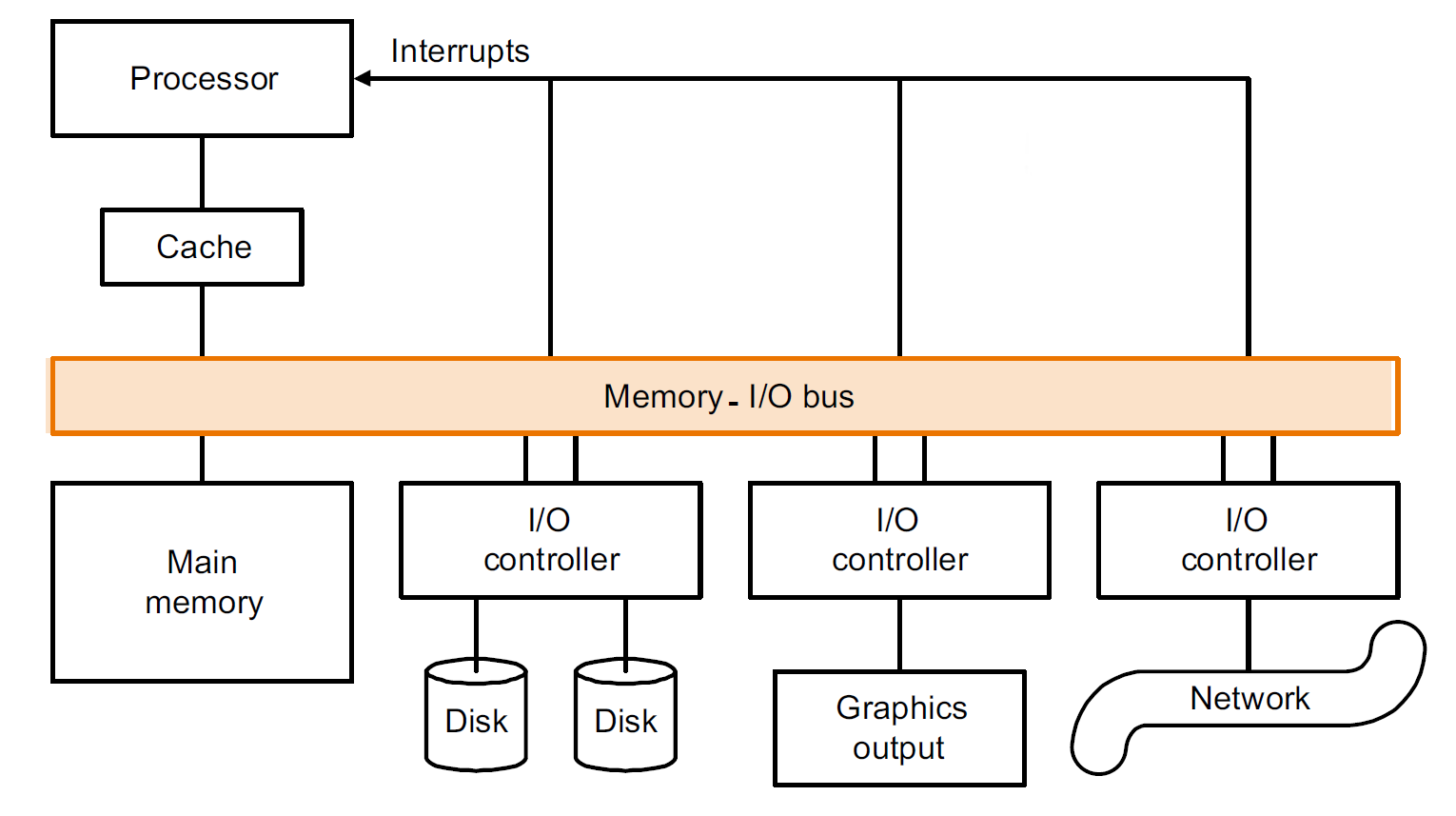

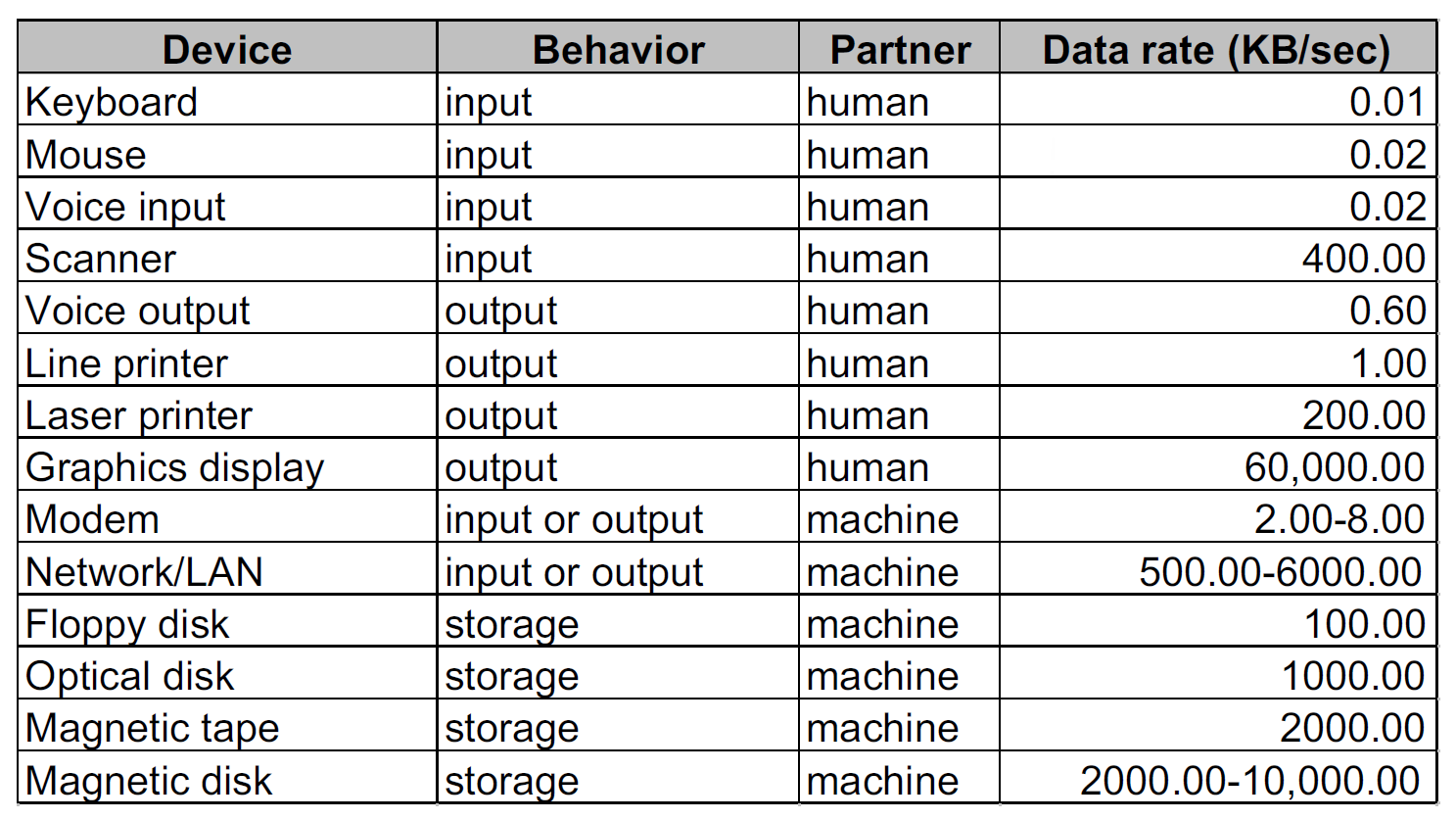

典型的 I/O 设备连接模型

I/O 设备的三大特性:

- 行为(behavior):输入(仅读一次

) 、输出(仅写一次,不可读)或存储(可重读或重写) - 搭档(partner):I/O 设备的另一端可以是机器,也可以是人类

- 数据(传输)速率(data rate):比如 I/O 设备与主存或处理器之间传输数据时的峰值速率

下表展示了不同 I/O 设备的三大特性的数据:

Disk Storage and Dependability⚓︎

见 Chap 5 最后的 Supplements。

Buses and Other Connections⚓︎

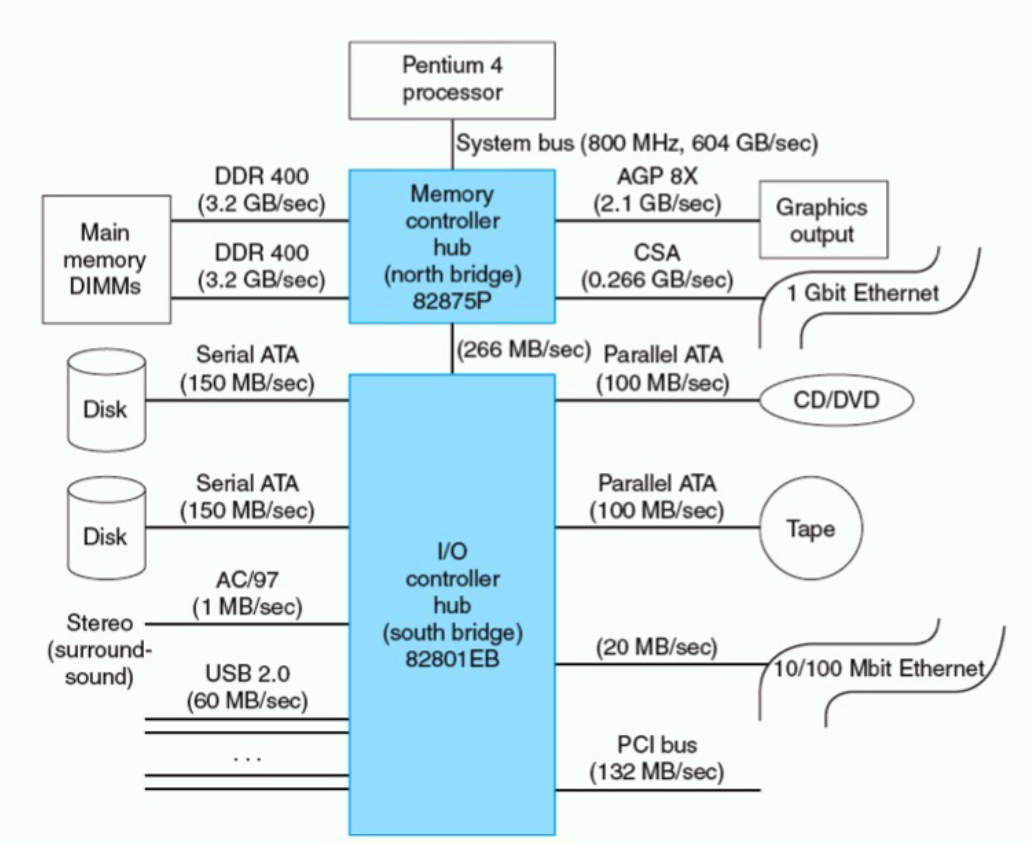

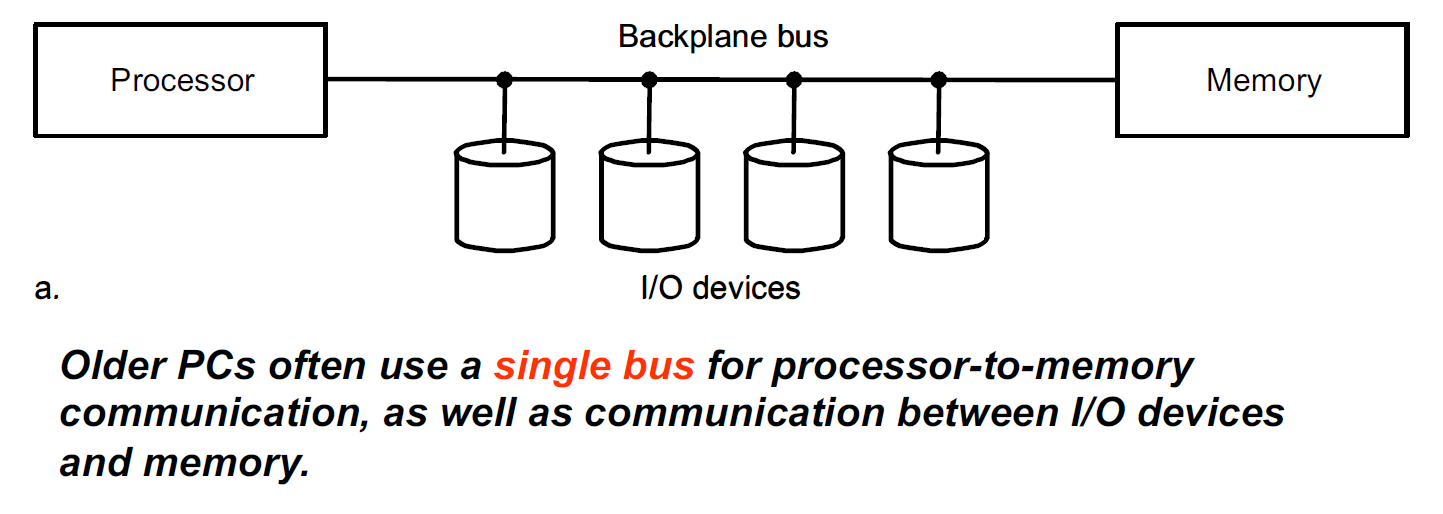

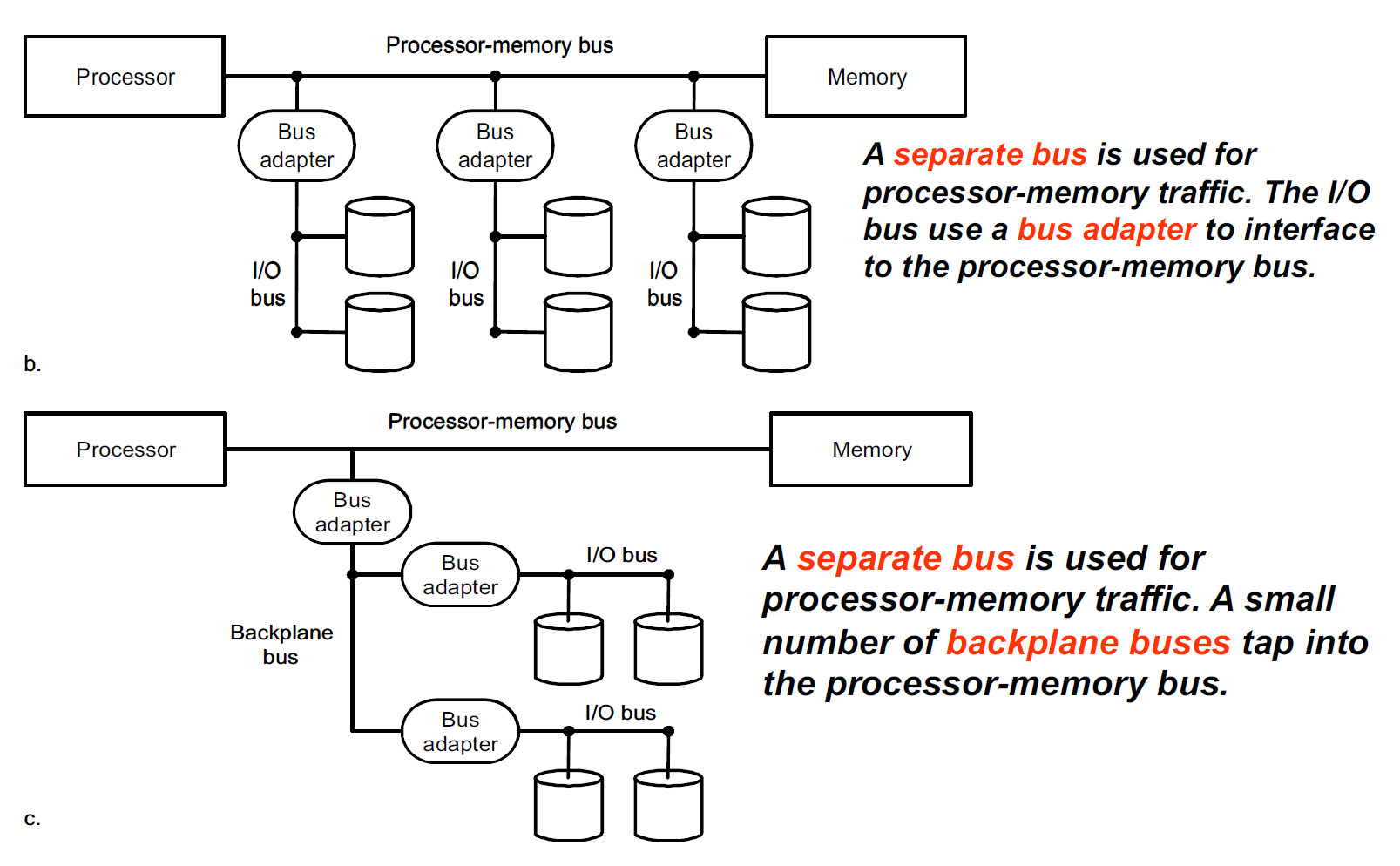

总览:

总线(bus):共用的通信连接(包含一根或多条线路)

-

总线包含两类线路:

- 控制线路:信号的请求 (request) 和确认 (acknowledgement),并表明数据线路上信息的类型

- 数据线路:在源和目的之间传递信息(数据、地址、复杂命令等)

-

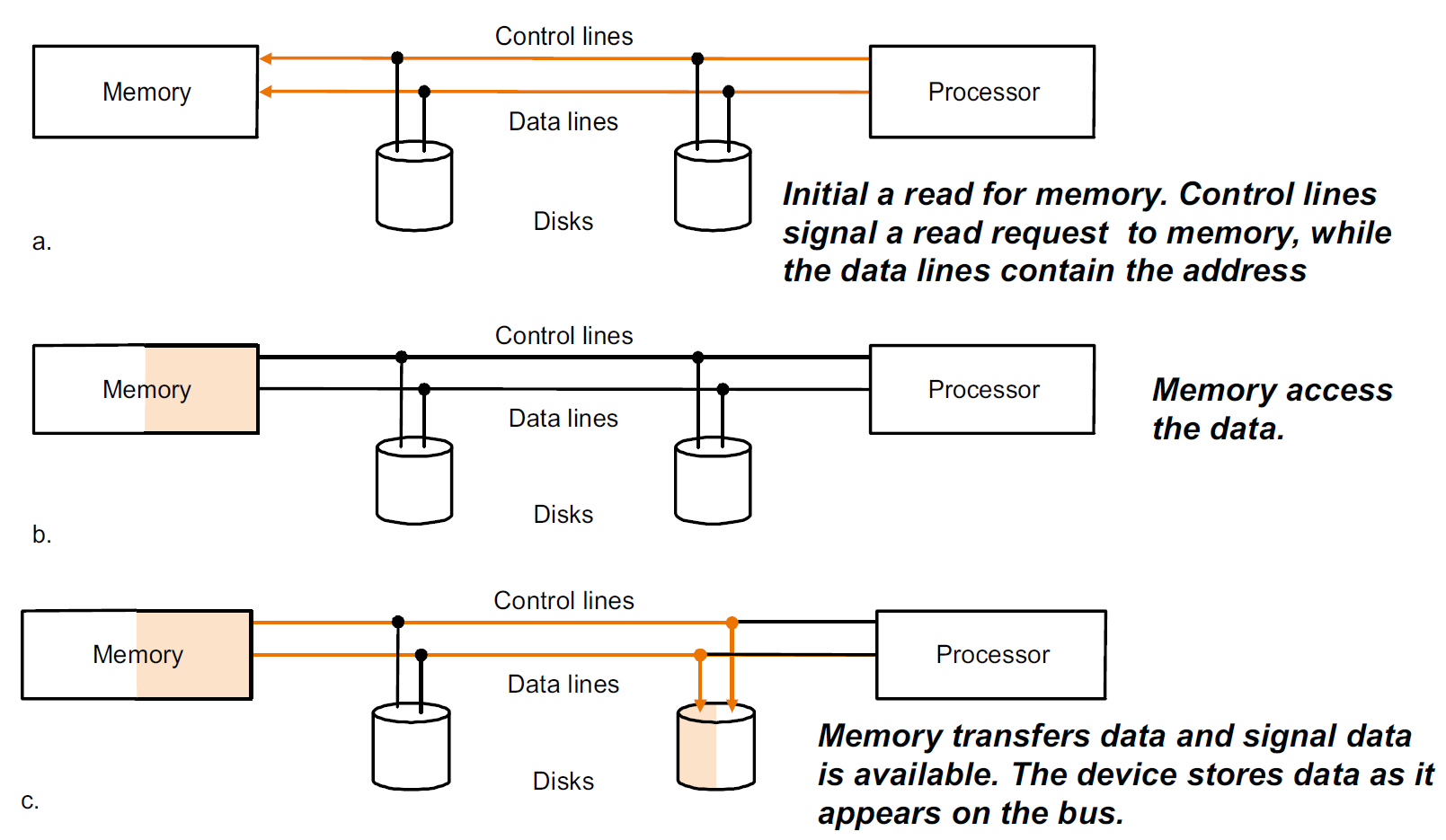

总线事务(transaction):发送地址,以及接收或发送数据

-

输出操作

-

输入操作

-

-

总线类型:

这三种模型的共同组成部分有:

- 处理器 - 内存:较高的速度,个性化设计

- 底板 (backplane):高速,标准化设计

- I/O:低速,不同设备,标准化

-

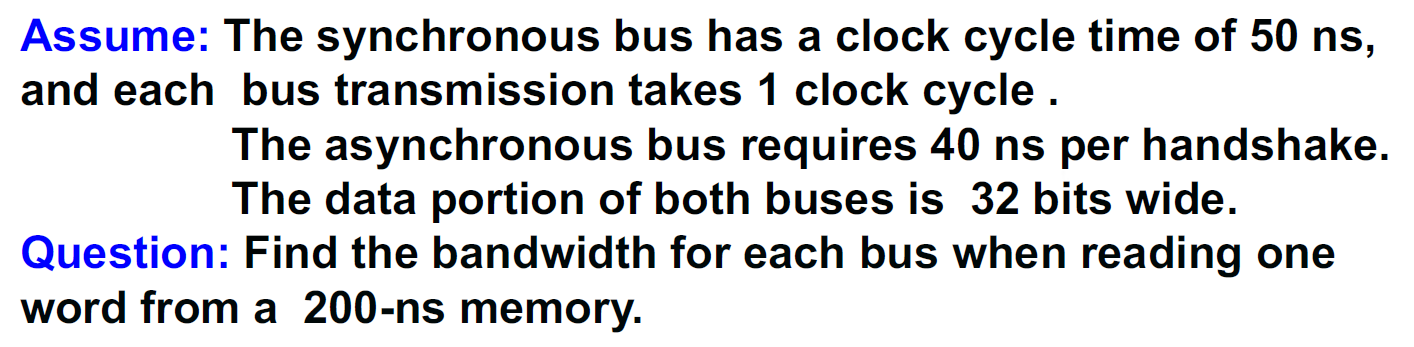

同步 (synchronous) 和异步 (asynchronous)

- 同步总线:使用时钟和固定的协议,快而小,但是所有设备需要保持相同的运作速率,且为避免时钟偏斜 (clock skew) 问题,总线需要短一些

-

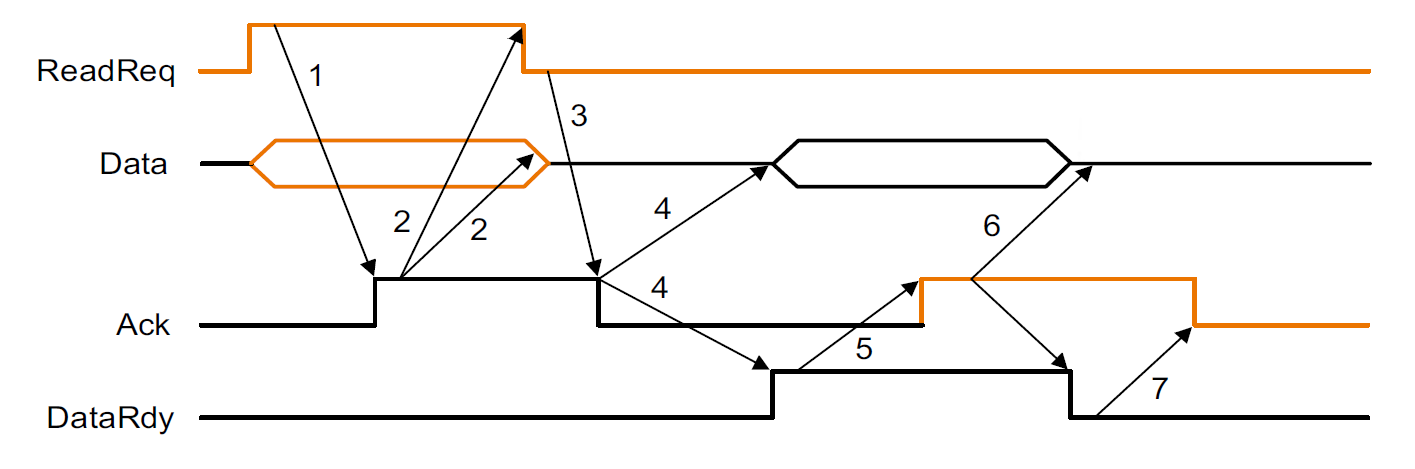

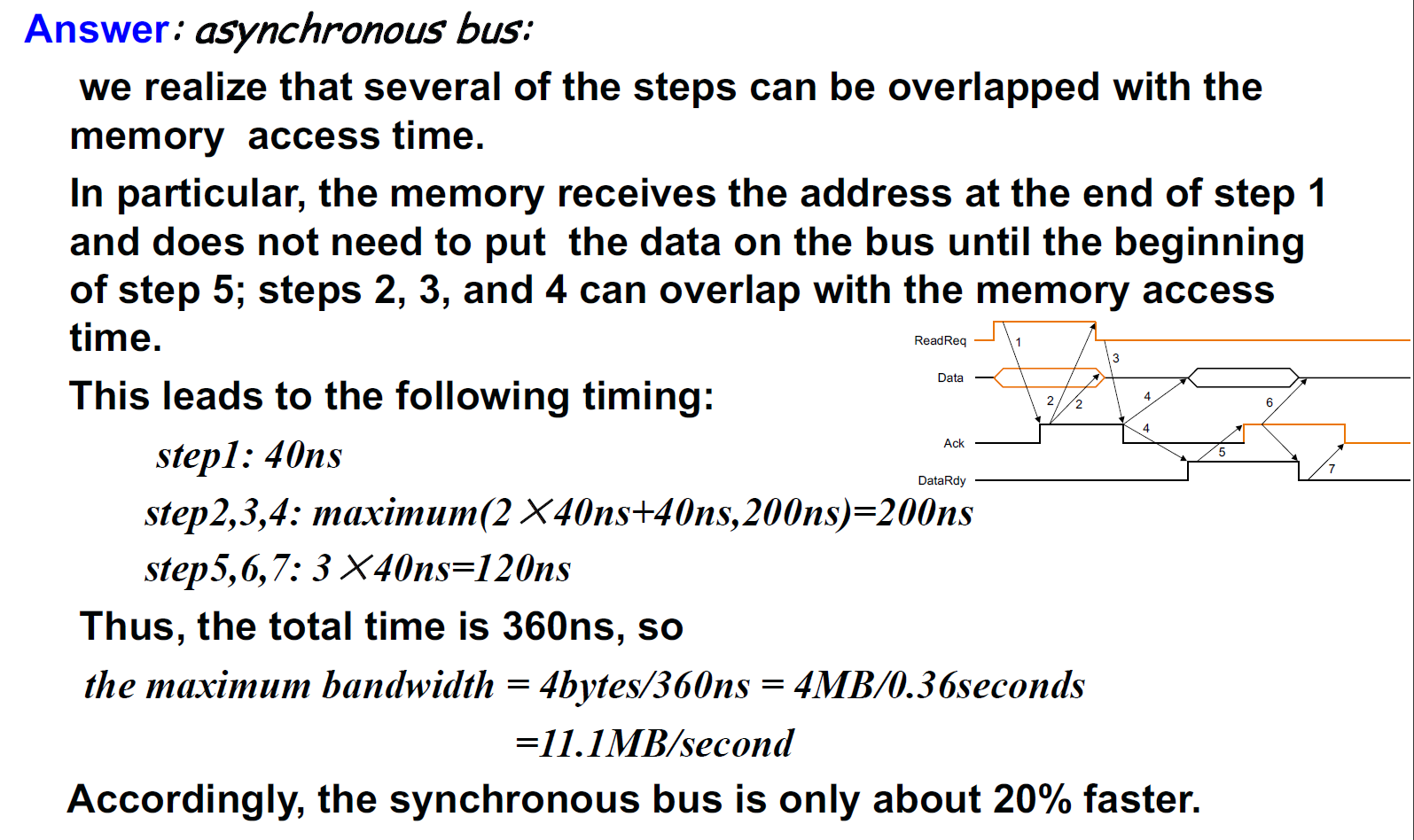

异步总线:不用时钟,而采用握手协议 (handshaking protocol)——一种用于协调异步总线传输的串行步骤,下面介绍具体过程:

- 当

ReadReq处于高电平时,内存从数据总线中读取地址,执行读操作,然后抬高Ack的电平,告诉设备它看到了ReadReq信号 - I/O 设备看到

Ack处于高电平后,将ReadReq置于低电平状态 - 内存看到

ReadReq处于低电平后,将Ack置于低电平状态 - 当内存完成数据读取后,它将数据放在数据线路上,并抬高

DataRdy的电平 - I/O 设备看到

DataRdy处于高电平后,将从总线中读取数据,然后抬高Ack电平来表明 I/O 设备完成对数据的读取 - 内存看到

Ack处于高电平后,将DataRdy置于低电平状态 - I/O 设备看到

DataRdy处于低电平后,将Ack置于低电平状态,表明完成了整个传输过程

- 当

-

两者的性能比较:

-

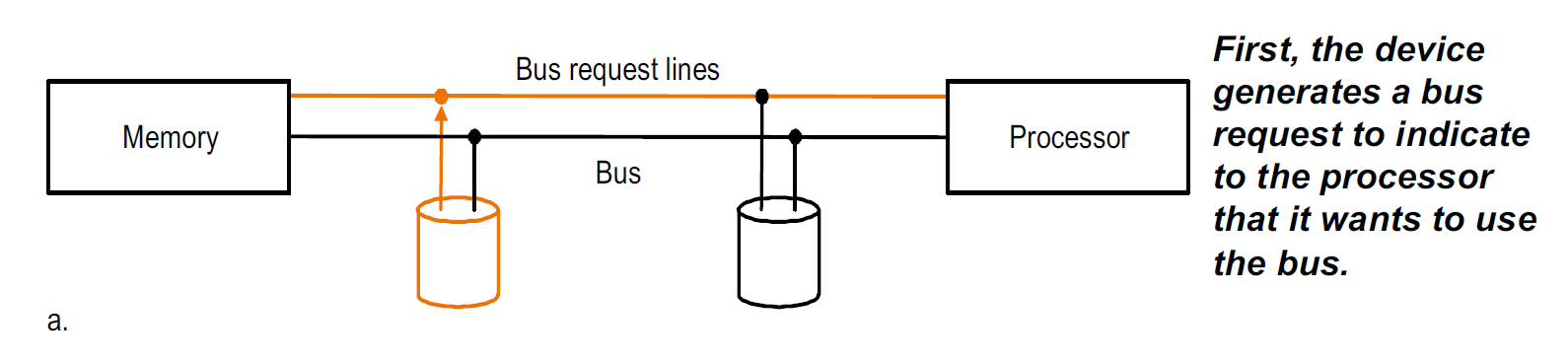

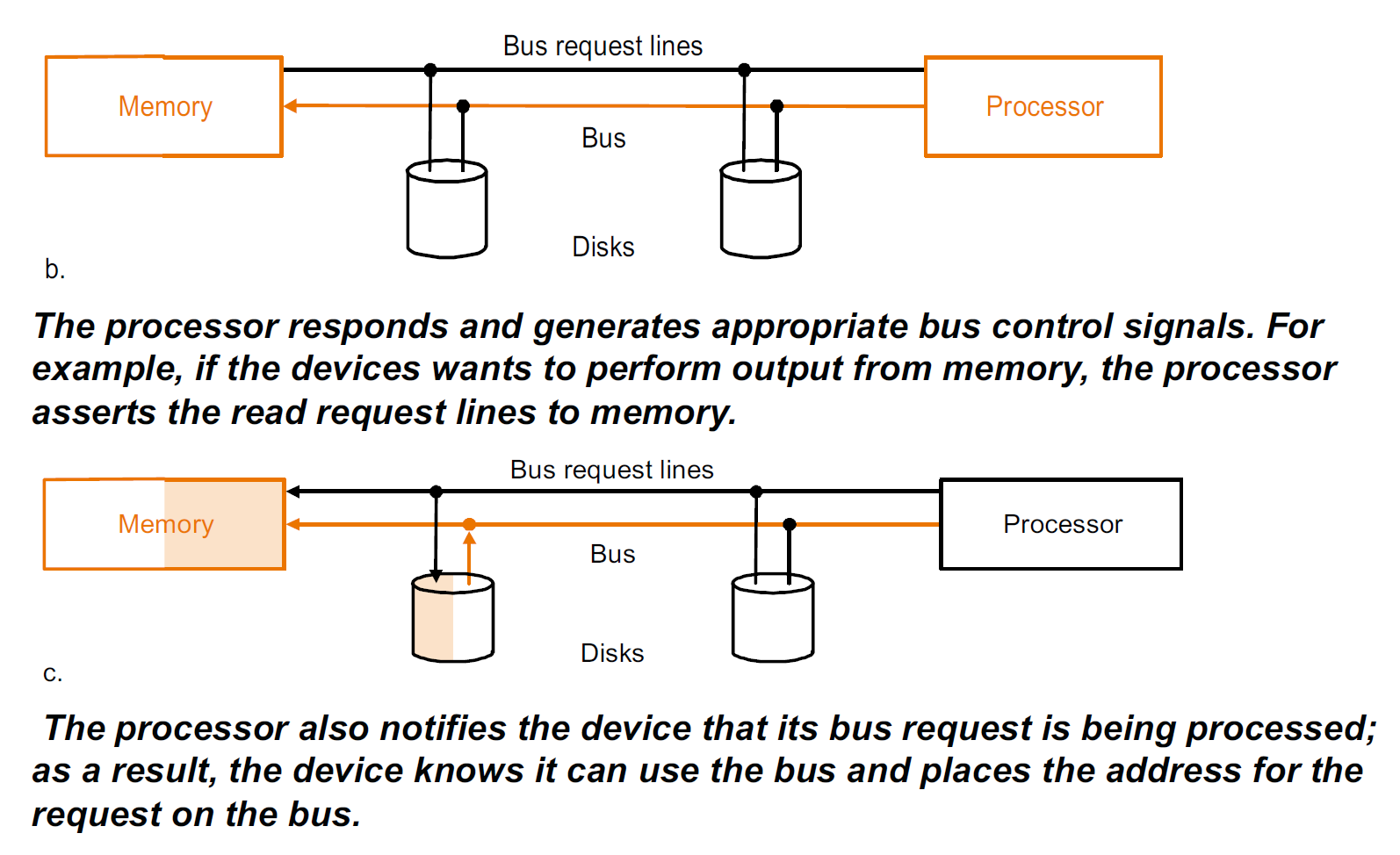

总线仲裁(bus arbitration)

- 如果不加任何控制,许多设备都期望获得对控制 / 数据总线的控制权,以便实现自己这部分的数据传递,这样显然会出乱子

- 因此需要用一个总线控制器(bus master) 来发起和控制所有的总线请求

-

方案:

- 菊式链 (daisy chain) 仲裁

- 集中 (centralized) 并行仲裁

- 自选 (self selection)

- 冲突检测 (collision detection)

-

为设备分配总线需要考虑的因素:总线优先级、公平性 (fairness)

-

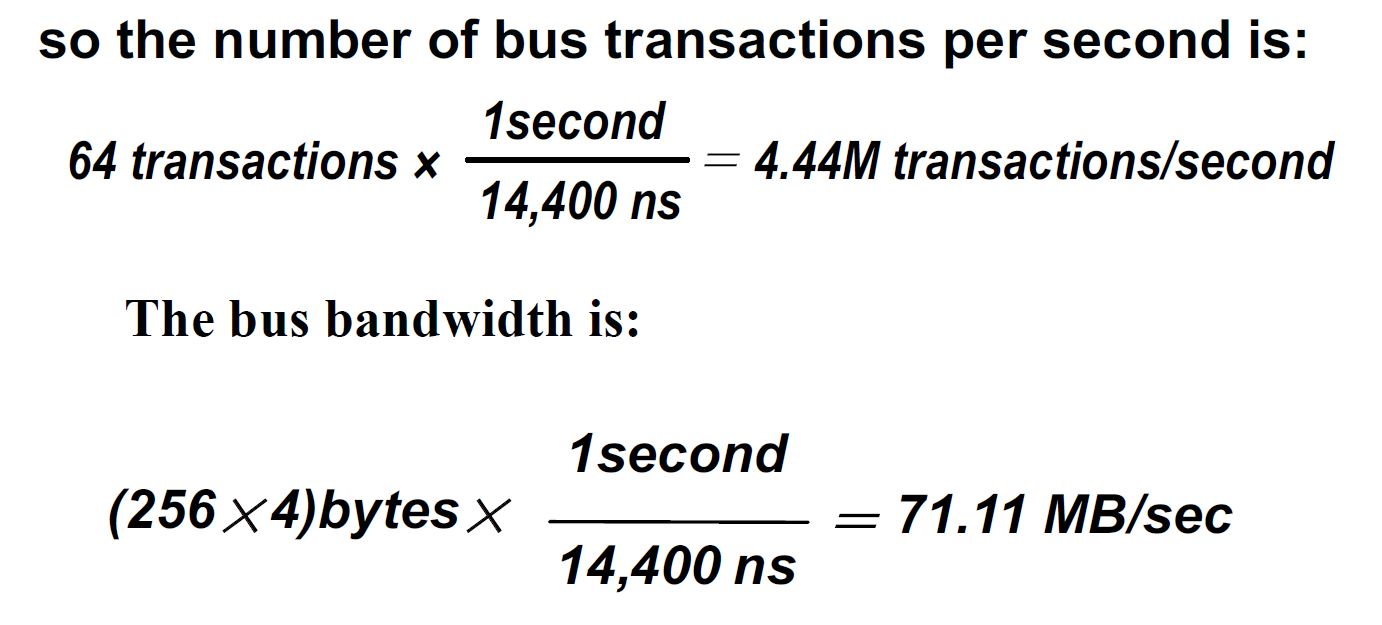

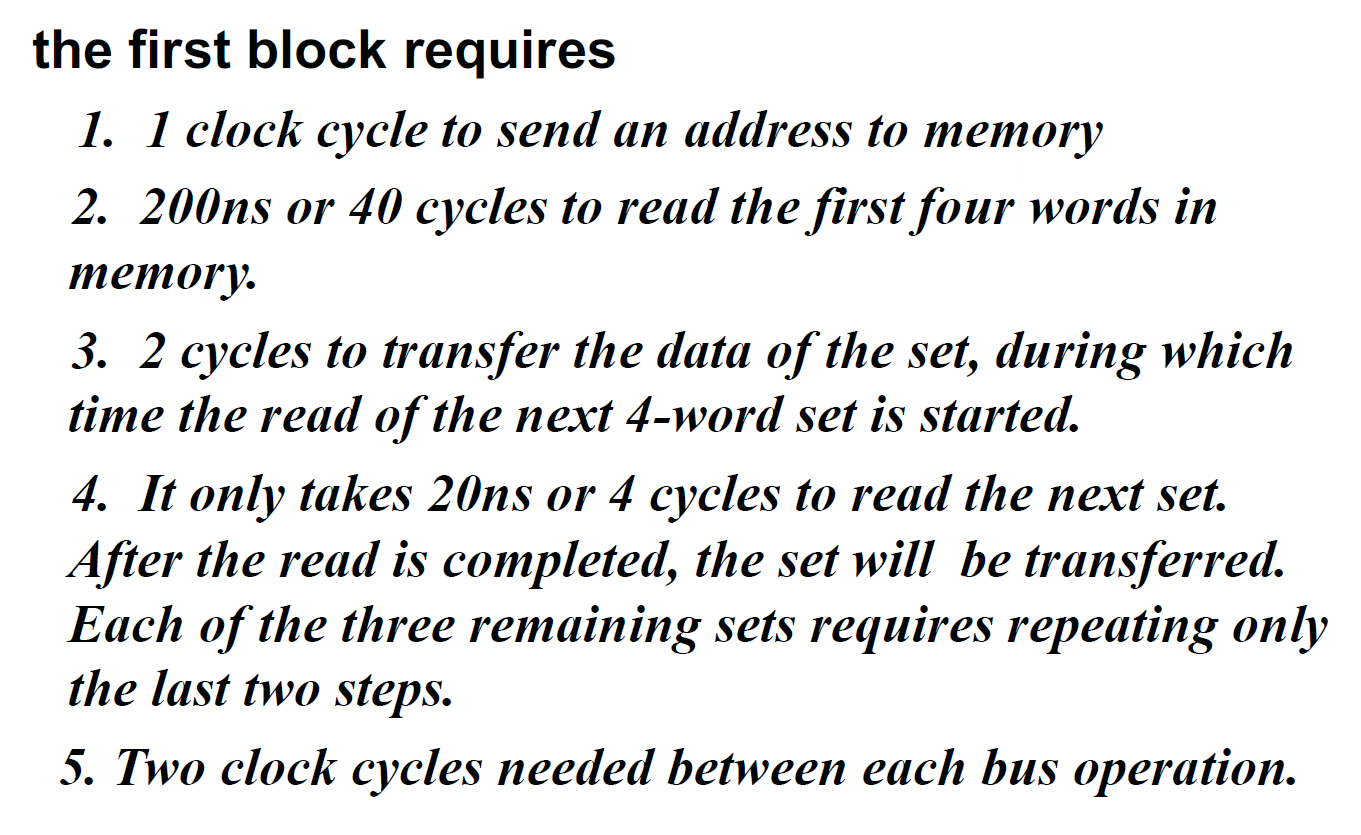

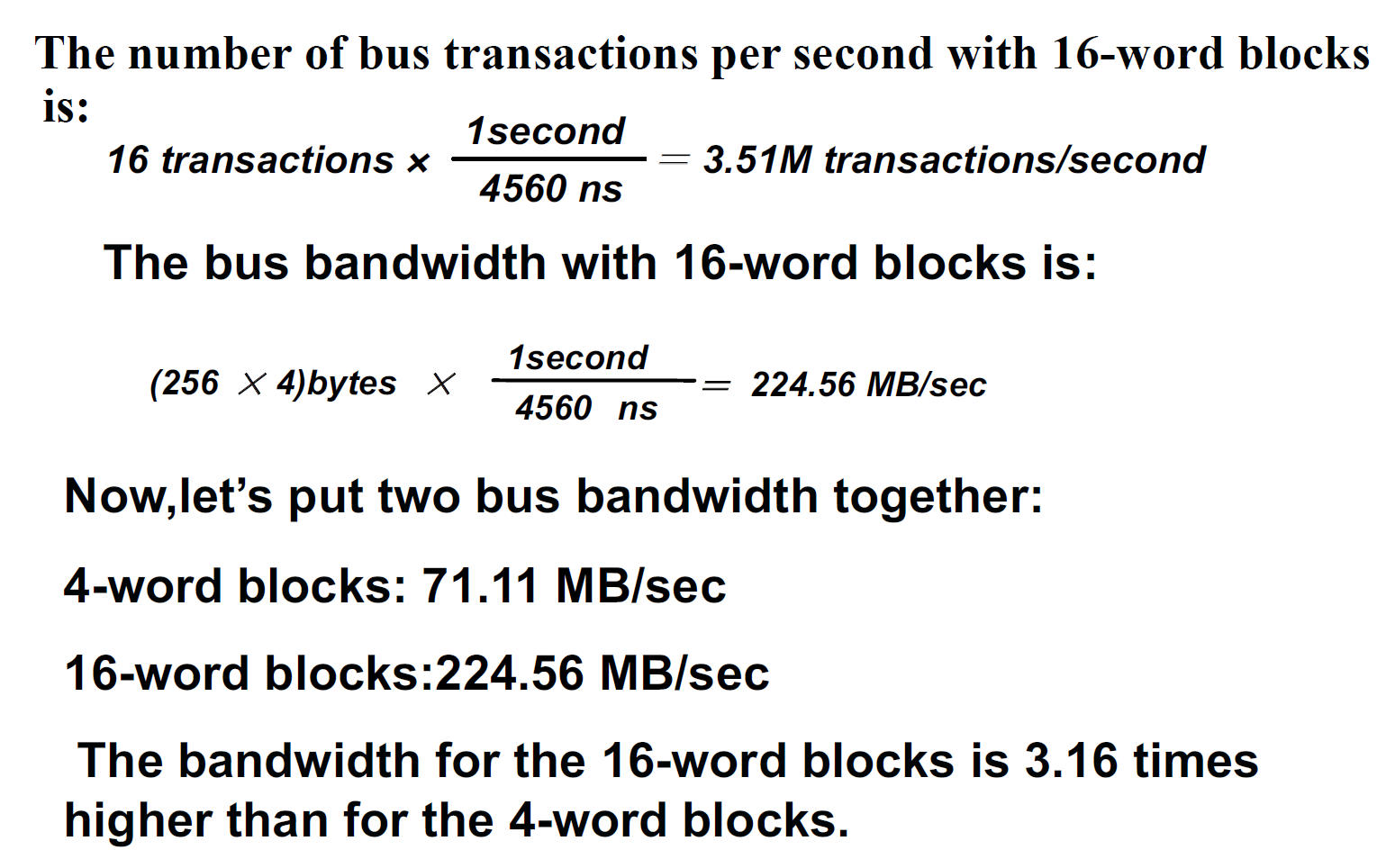

增加带宽 (bandwidth)

Interface⚓︎

I/O 系统的三大特征:

- 多个程序共用 (share)I/O 系统

- 通常使用中断(interrupt) 来实现 I/O 操作的信息传递 (communicate)

- 必需的传递类型有:

- OS 必须能够为 I/O 设备提供命令(commands)

- 内存映射 I/O:部分的内存地址空间会被分配给 I/O 设备,且

lw和sw指令能够访问 I/O 端口 - 特殊 I/O 指令

- 输入:

in al, port - 输出:

out port, al

- 输入:

- 命令端口、数据端口

- 状态寄存器(记录完成位 (done bit)、错误位 (error bit) 等)

- 数据寄存器、命令寄存器

- 内存映射 I/O:部分的内存地址空间会被分配给 I/O 设备,且

- 当 I/O 设备完成操作或遇到错误时,必须通知(notify)OS

- 数据必须在内存和 I/O 设备之间传输

- OS 必须能够为 I/O 设备提供命令(commands)

- 必需的传递类型有:

- 对 I/O 设备的底层控制较为复杂

处理器与 I/O 设备之间的通信:

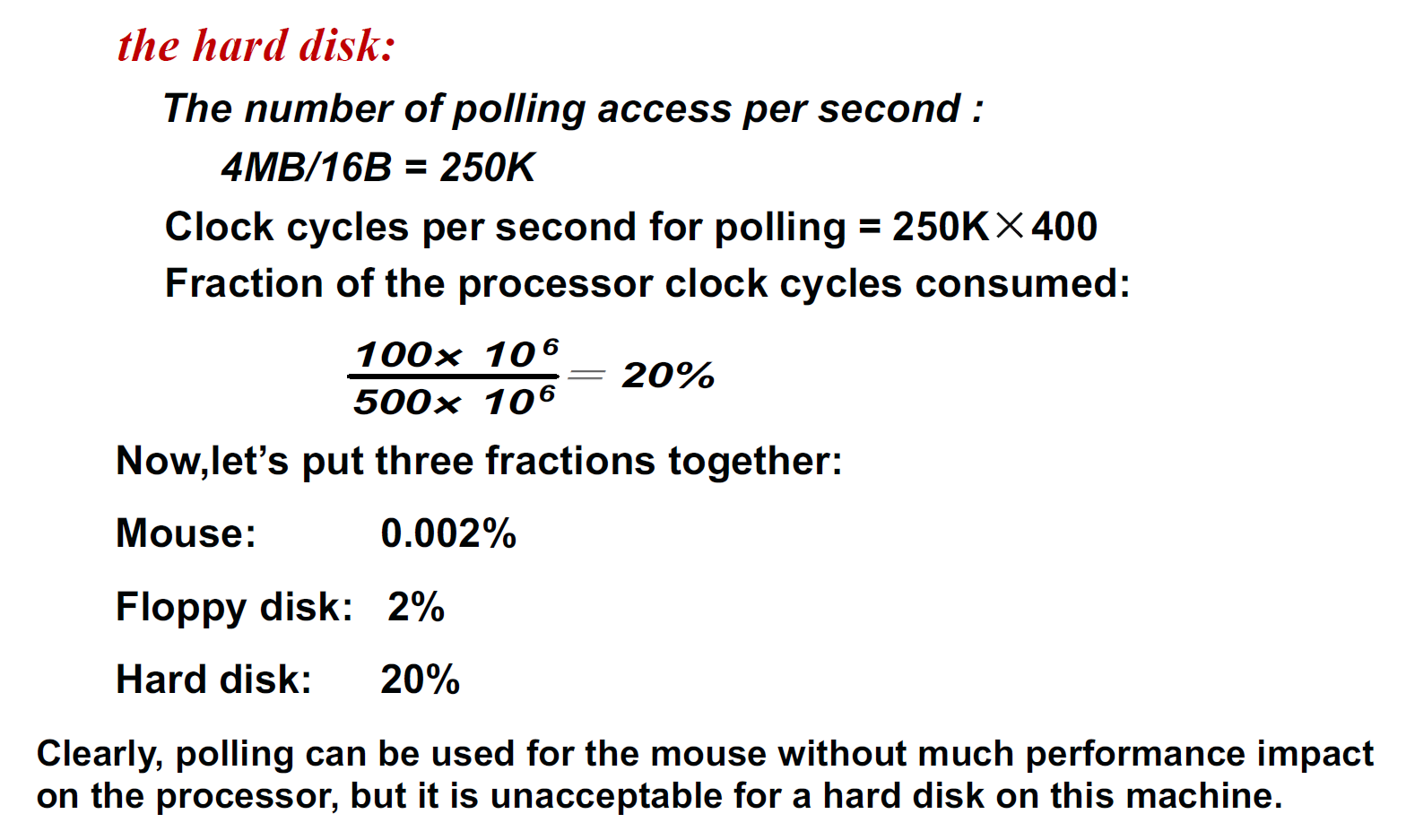

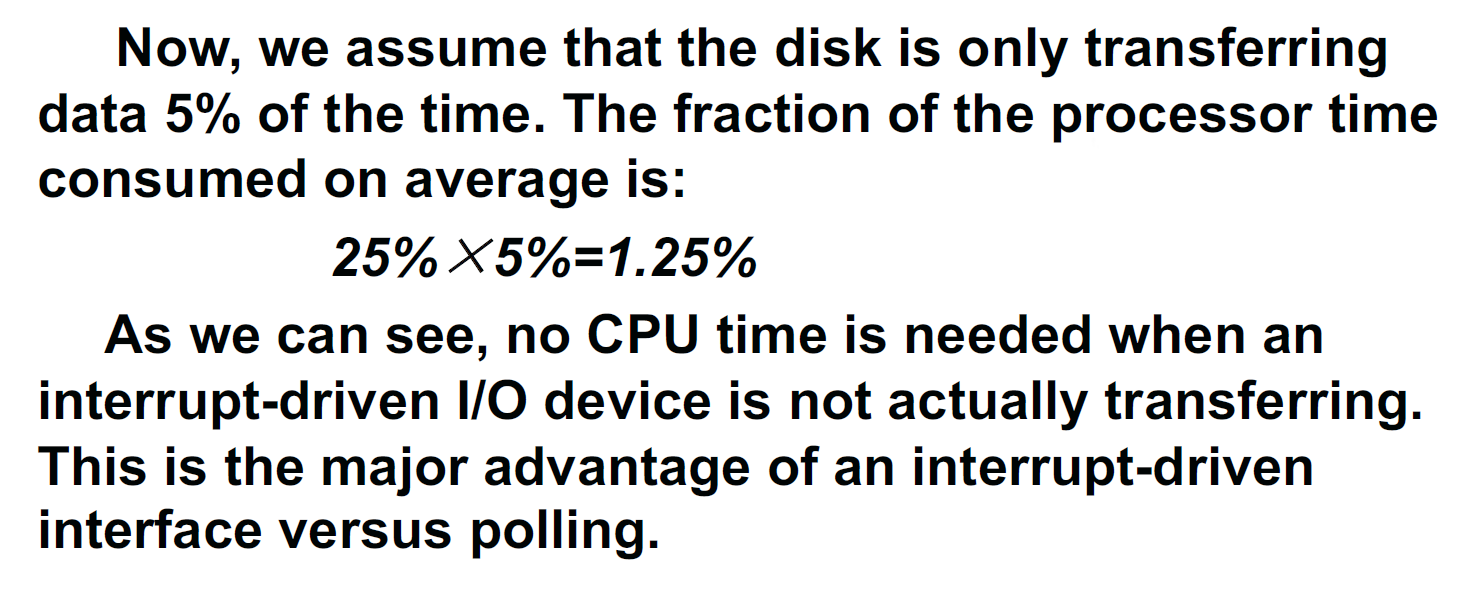

- 轮询(polling):处理器周期性地检查状态位,观察当前是否需要进行下一步 I/O 操作

- 缺点:浪费大量的处理器时间

-

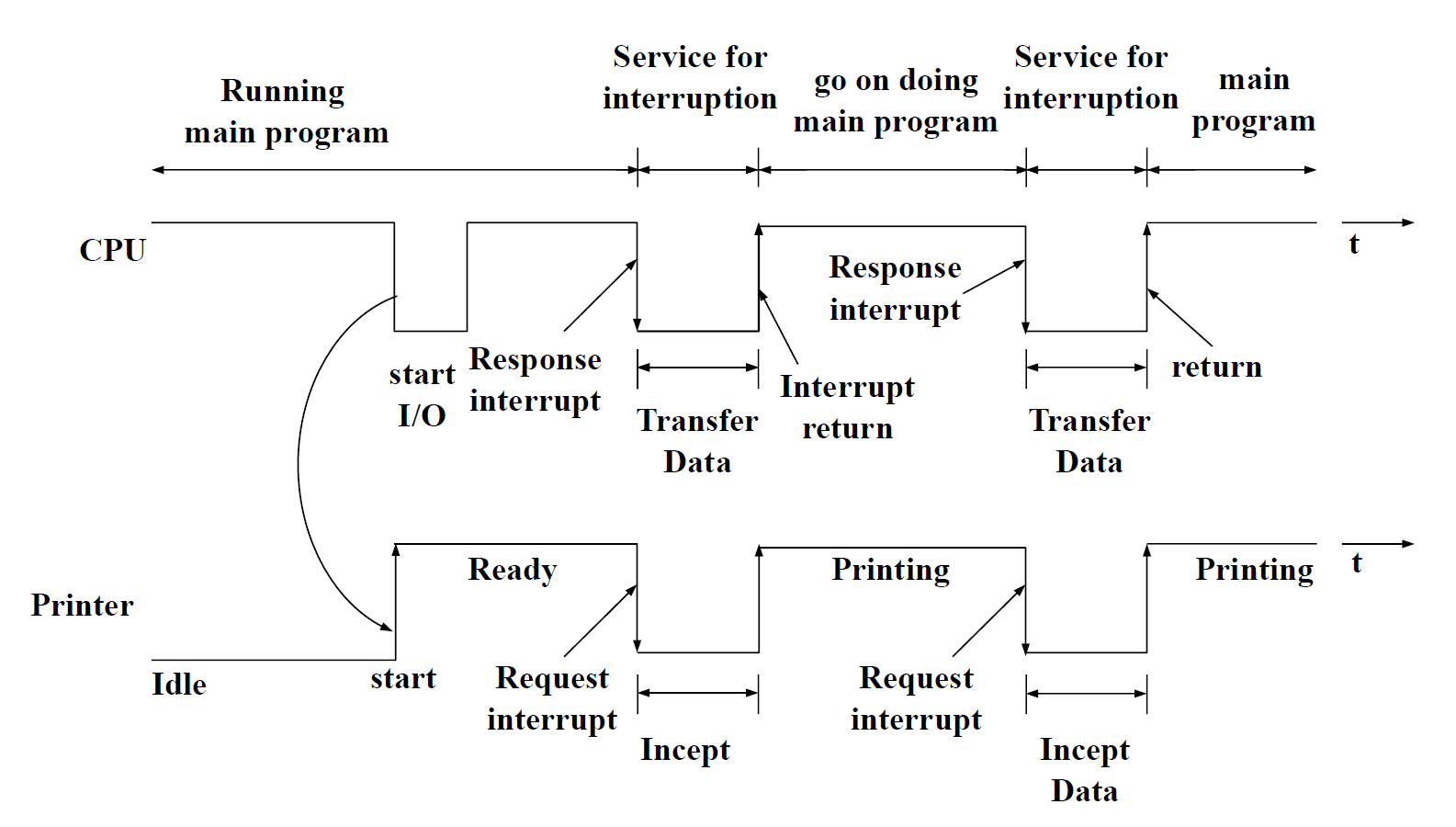

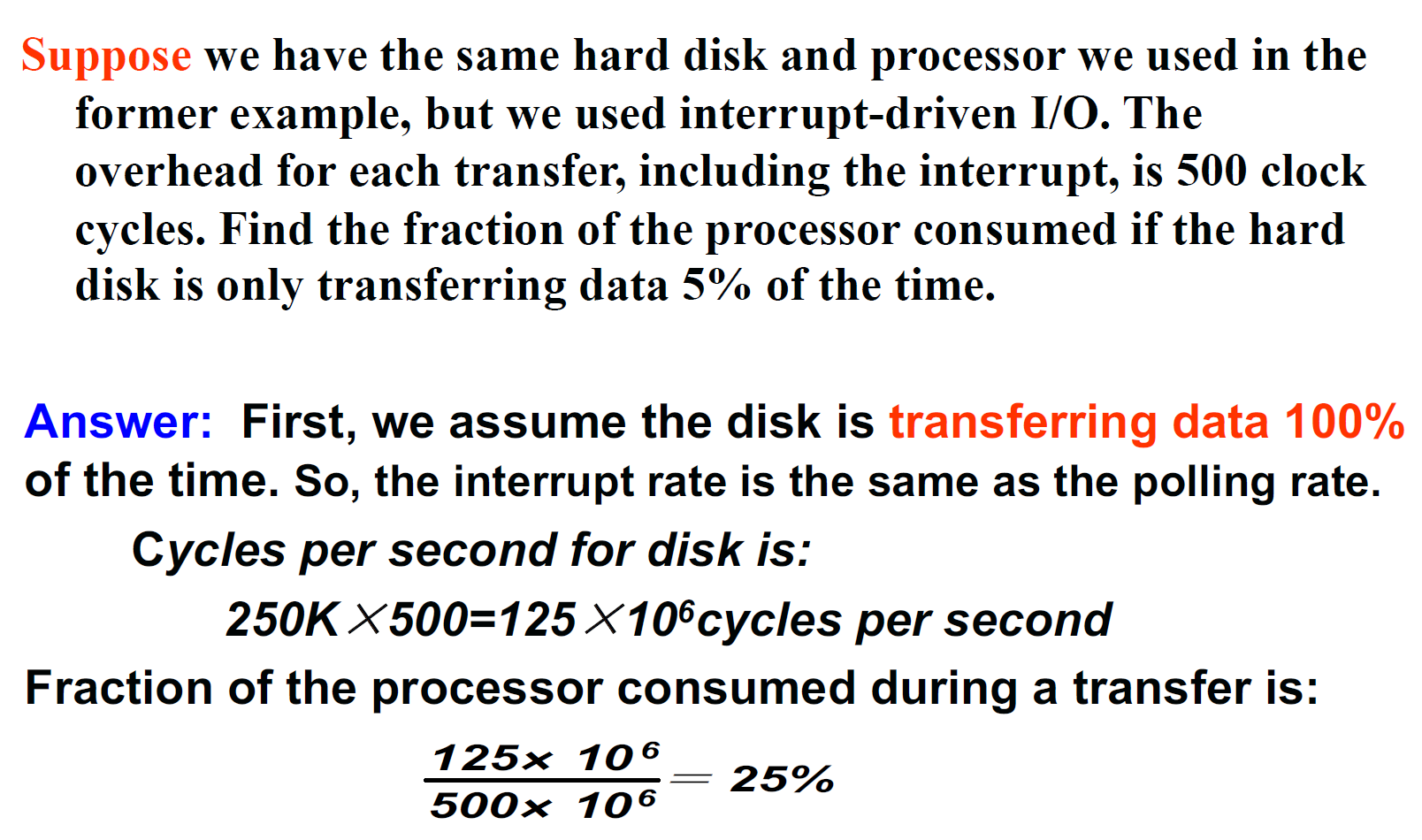

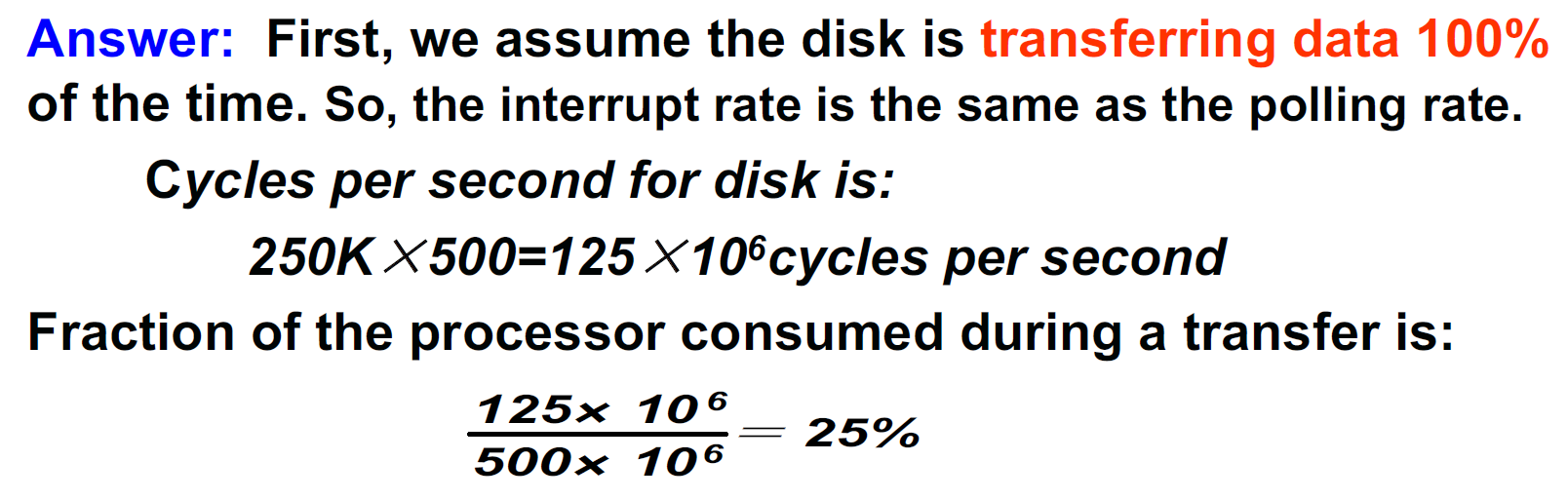

中断(interrupt)

- 中断驱动的 I/O 模式:它的优点是并发操作 (concurrent operation)

-

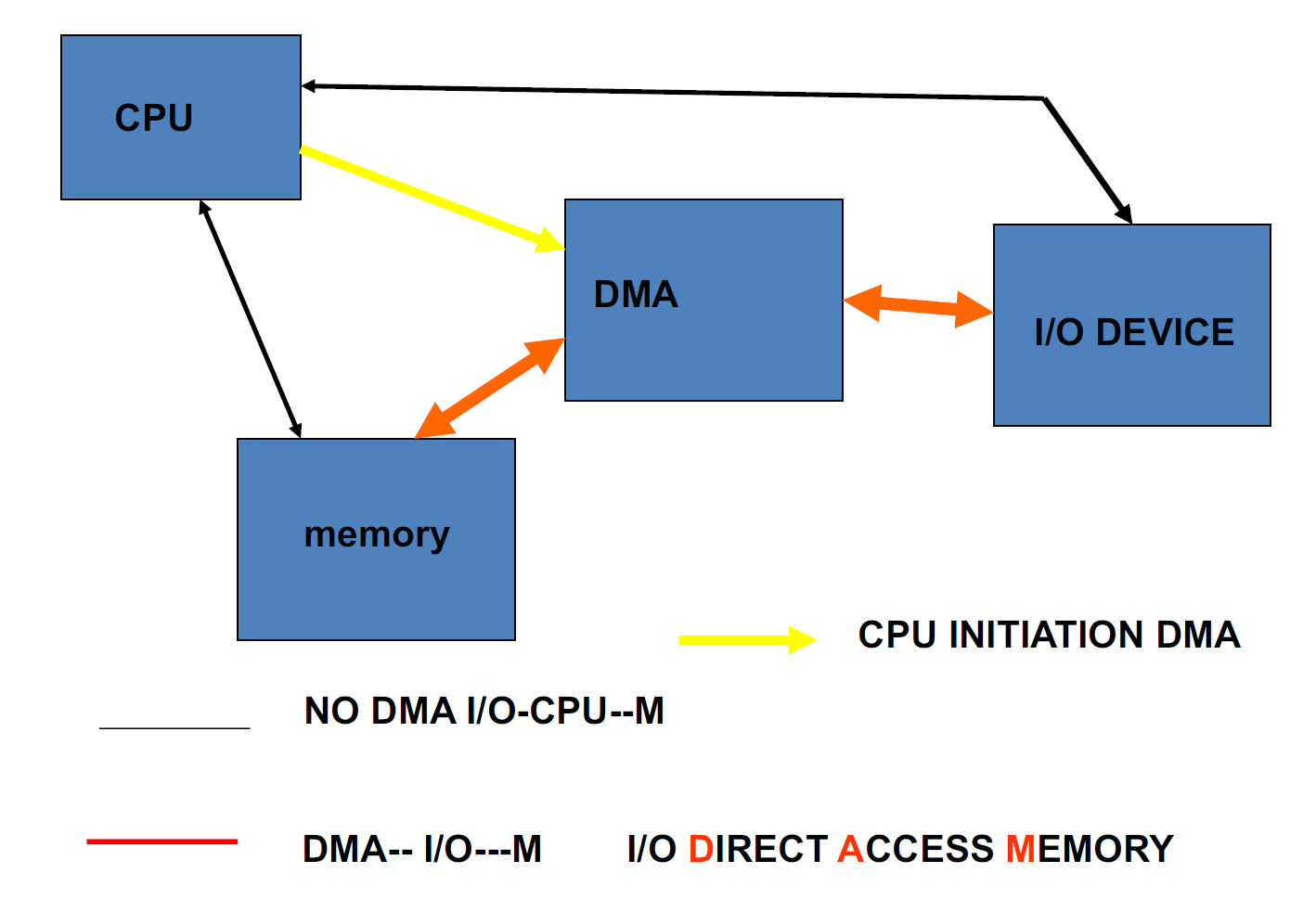

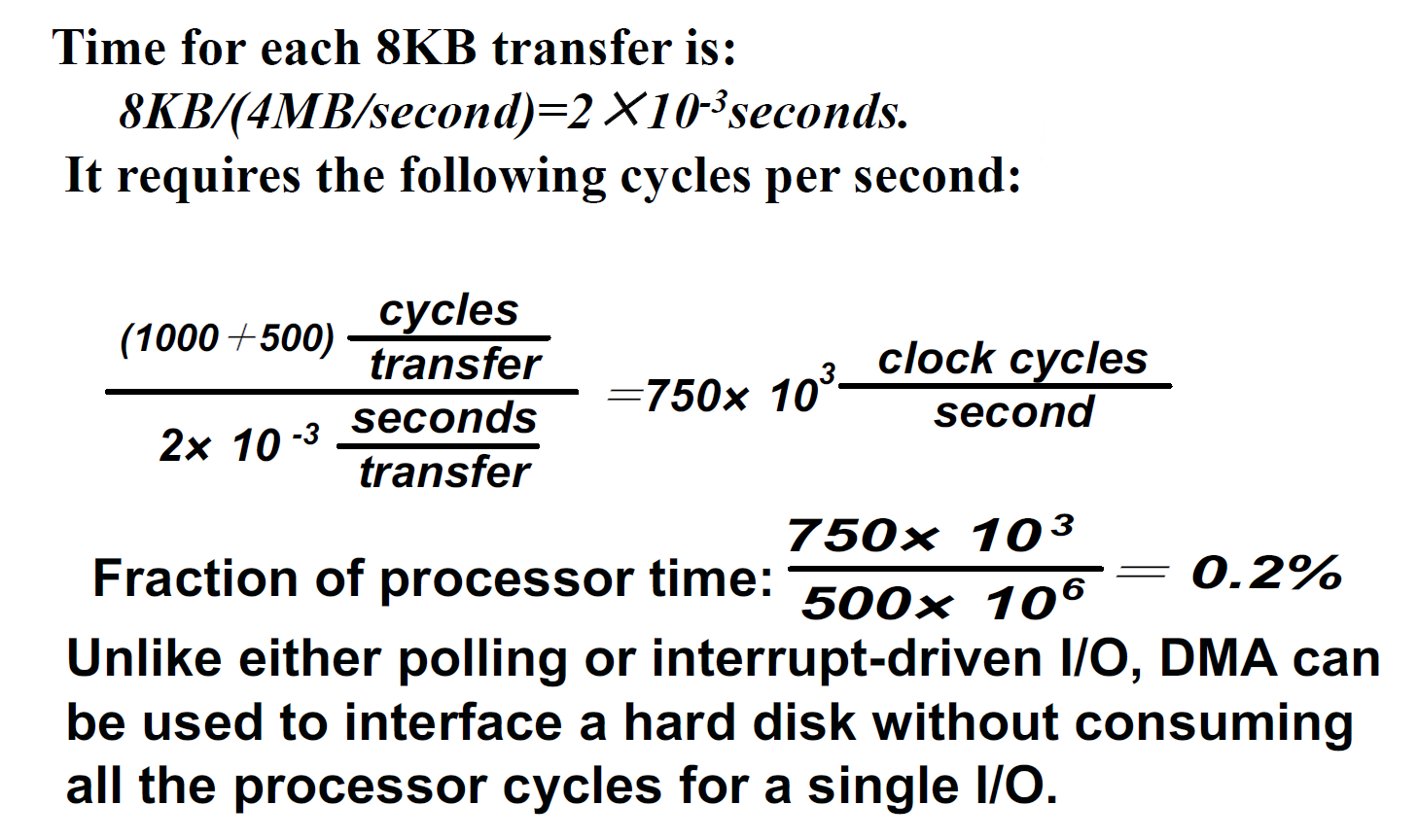

直接内存访问(direct memory access, DMA):设备控制器直接向 / 从内存传输数据,不需要处理器的介入

-

DMA 传输模式

- 首先处理器通过提供一些信息来设置 DMA 模式,具体包括:设备 ID、操作、待传输数据的内存源地址和目标地址、需要传输的字节数等

- DMA 开始执行操作,并对总线进行仲裁。若某个请求需要在总线上多次传输数据,那么 DMA 单元生成下一个内存的地址,并发起下一次传输

- 一旦 DMA 传输完成,控制器向处理器发起中断,随后检查是否发生错误

-

这种方式可以使 CPU 和 I/O并行工作,互不干扰

-

Performance Measurements⚓︎

几类关于 I/O 的基准测试 (benchmark):

- 超级计算机 I/O 基准测试

- 事务处理 I/O 基准测试

- I/O 速率:每秒访问硬盘的数量(数据速率的倒数)

- 文件系统 I/O 基准测试:包括 MakeDir、Copy、ScanDir、ReadAll、Make 操作等

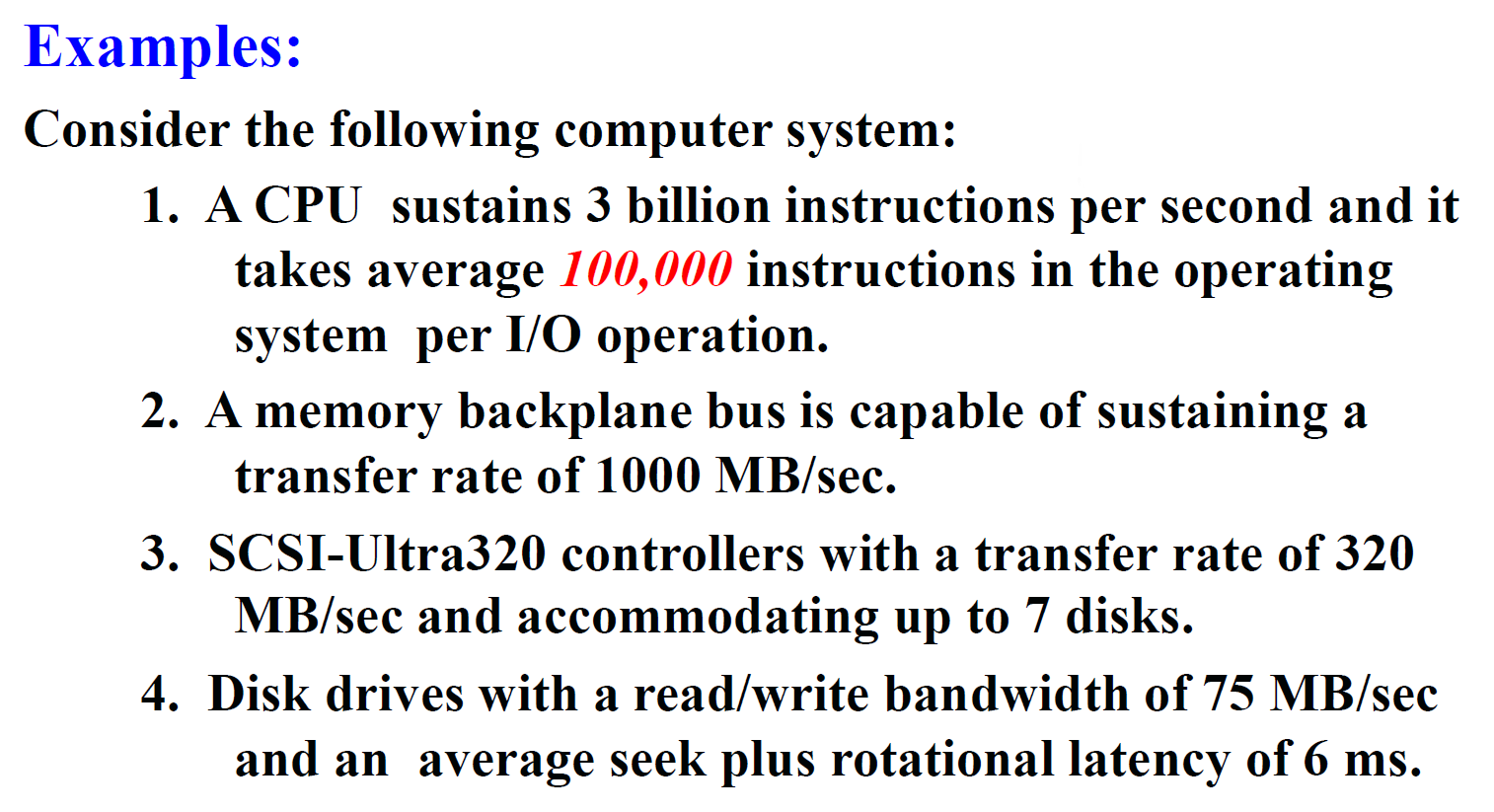

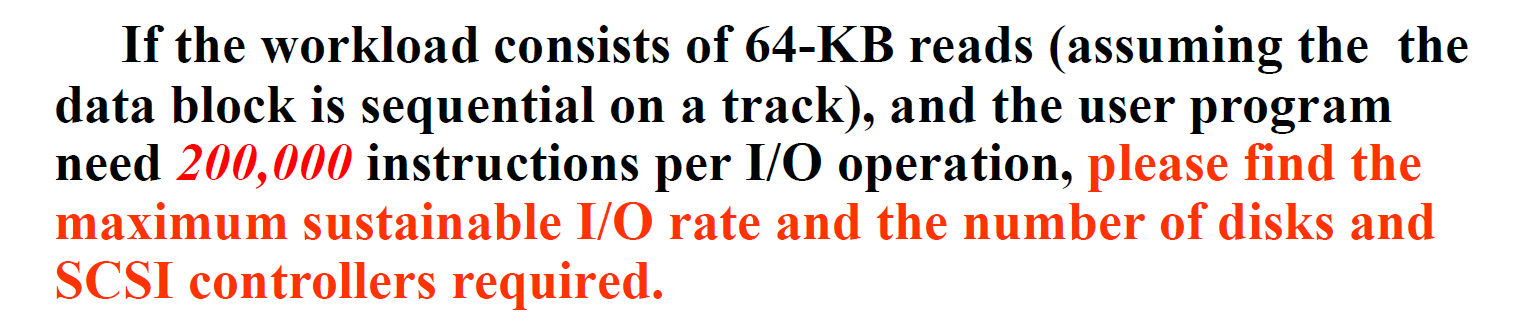

I/O System Design⚓︎

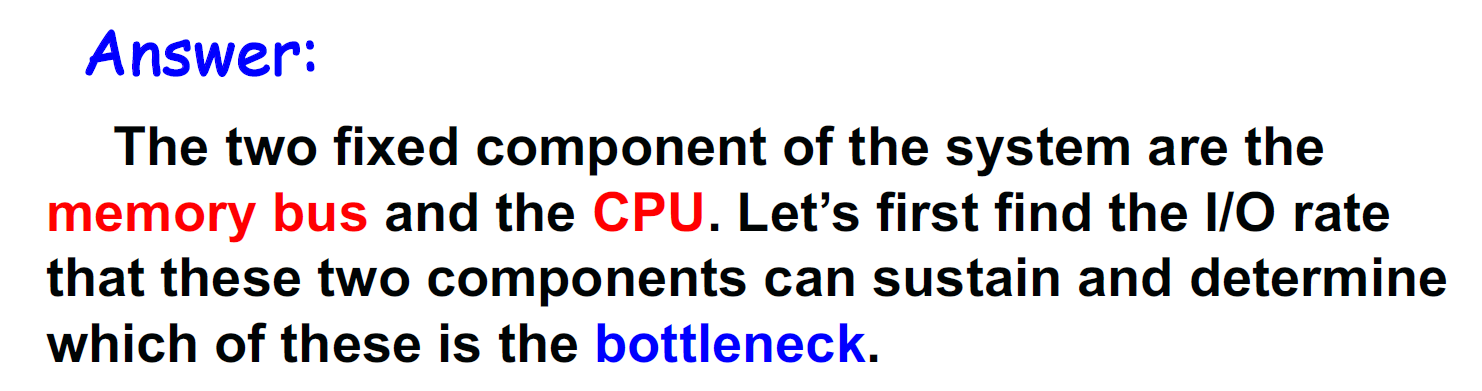

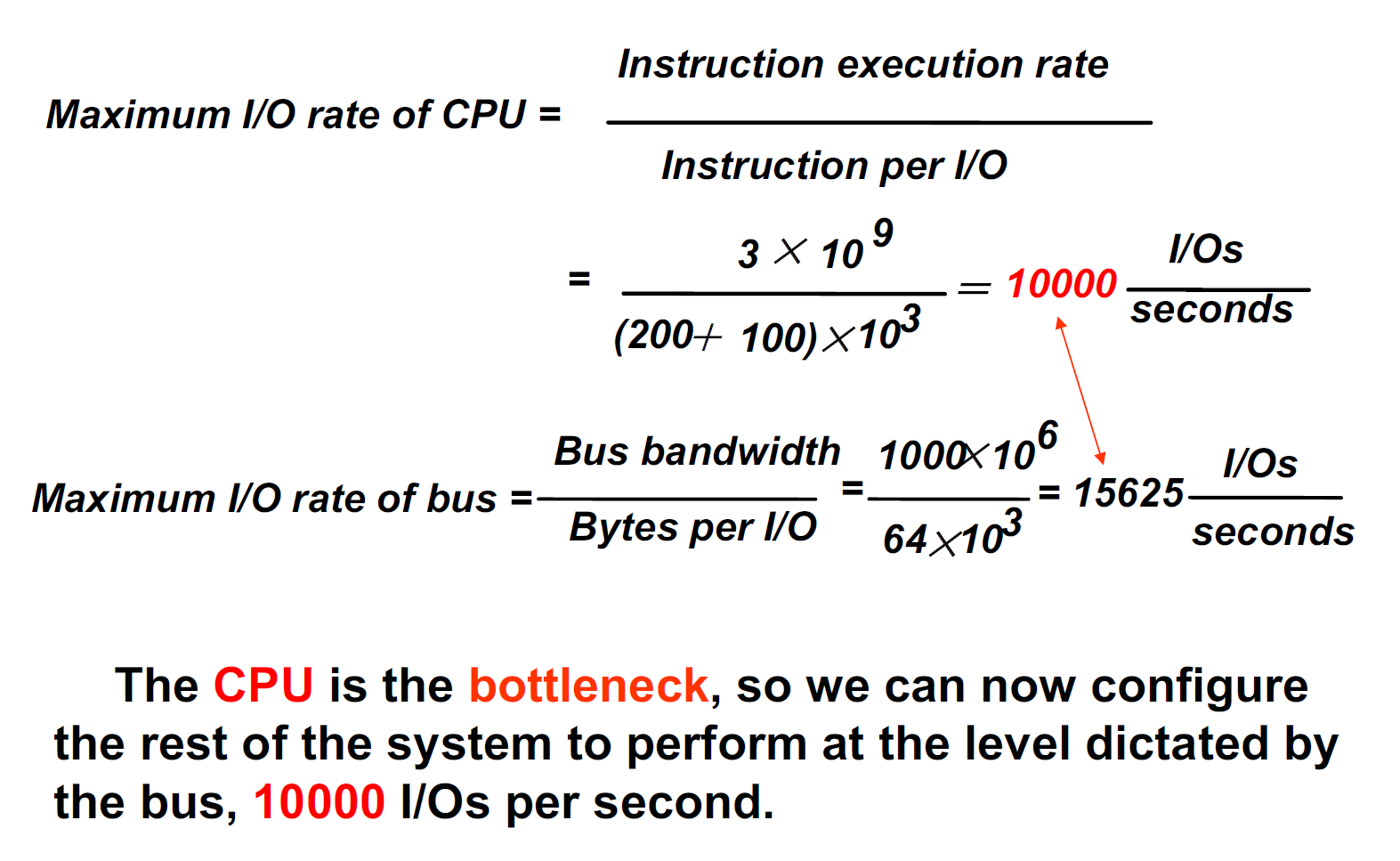

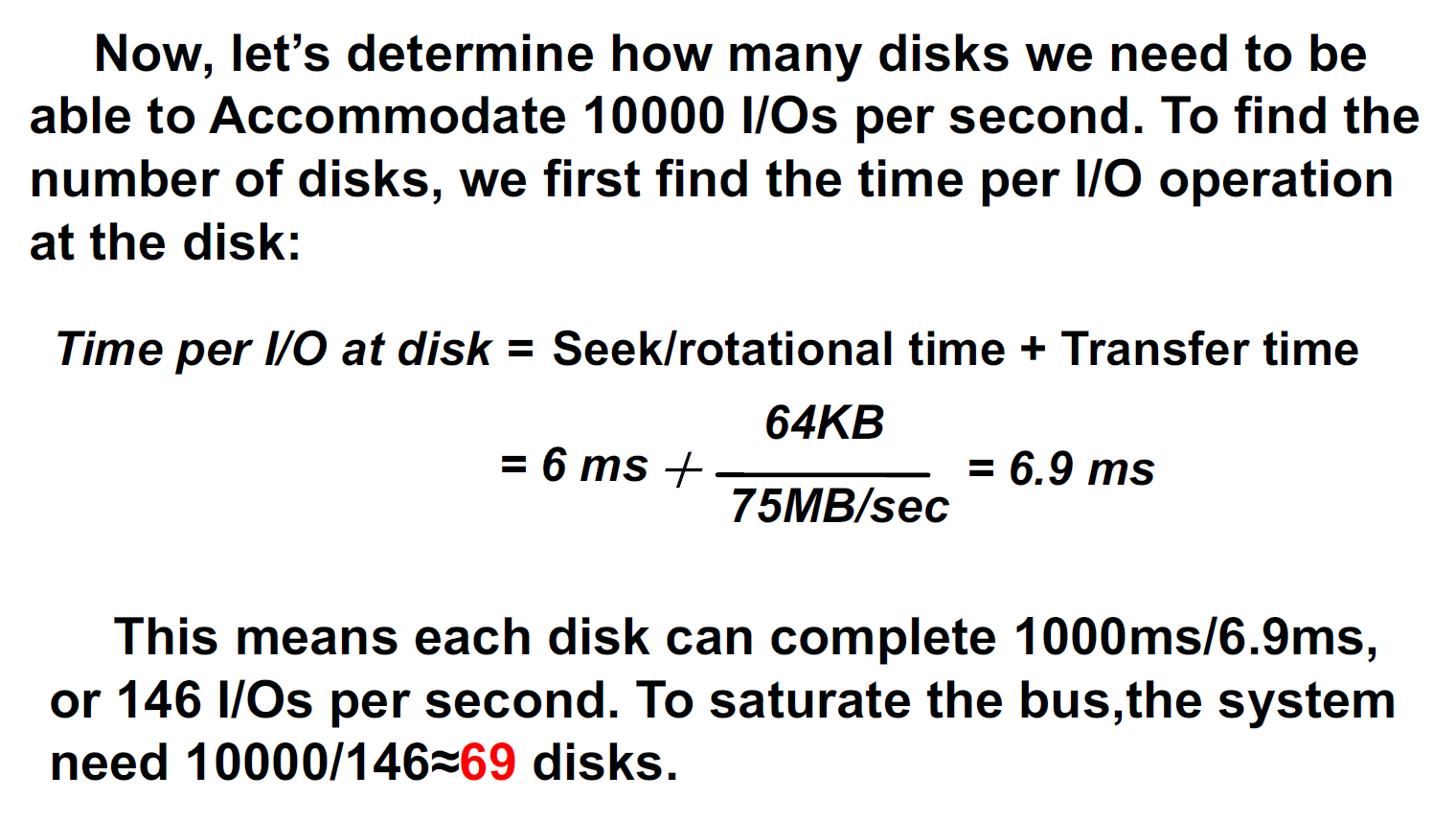

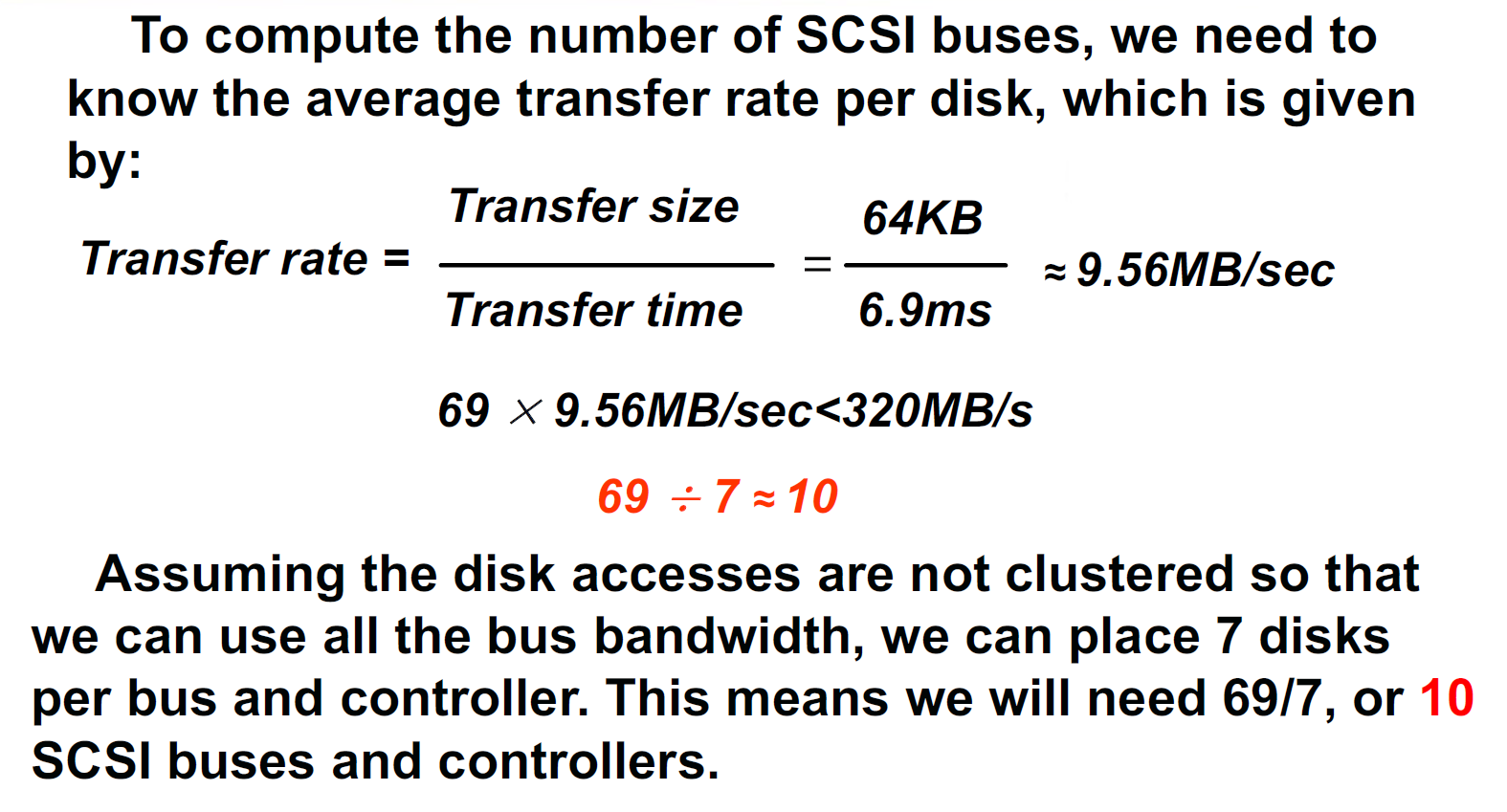

设计 I/O 系统的通用方法:

- 找到 I/O 系统最弱的连接,它是 I/O 通路上限制设计的一个组件。工作负载和配置限制都可以决定最弱链接的位置

- 通过配置该部件来维持所需带宽。确定系统其余部分的要求,并配置它们以支持此带宽

开怀一笑

"The difficulties in assessing and designing I/O systems have often relegated I/O to second class status..courses in every aspect of computing, from programming to computer architecture often ignore I/O or give it scanty coverage...textbooks leave the subject to near the end, making it easier for students and instructors to skip it!"

纯粹在骂自己

评论区